# Seymour CARY'S Reference Manual For the 7600

# CONTROL DATA® 7600 COMPUTER SYSTEM

Information presented in this edition is preliminary and subject to change. Any corrections necessitated by design changes and/or product improvement will be handled by standard manual revision procedures. Errors and suggestions should be communicated to Development Division, Technical Publications Dept.

# PRELIMINARY REFERENCE MANUAL

Most of the information in this manual was evaluable early in 1967. The 7600 prototype checkout began around and 1967. The first 7600 shipped 2/1/69

This document, along with expanded logic diagrams & wire lists, was used by the angineers when checking out the prototype, software people, the CE's during the early days of the 7600.

This mandal is: still used today by individuals in CDC's 7600 software support department.

#### FOREWORD

The ideas and designs set forth in this Control Data 7600

Preliminary Reference Manual are the property of Control Data

Corporation and are not to be disseminated, distributed, or conveyed to third persons without the express written permission of the

Control Data Corporation Patent Department.

# TABLE OF CONTENTS

# PART : SYSTEM DESCRIPTION

| Introduction 1             | L-0             |

|----------------------------|-----------------|

| System parameters          | L-1             |

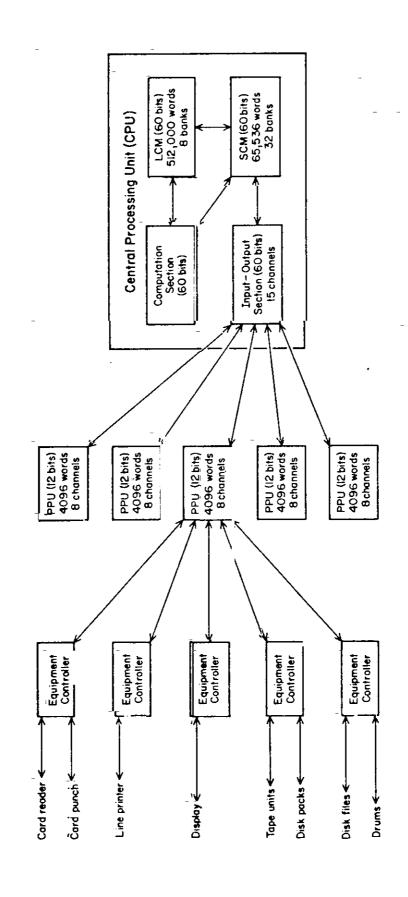

| System communication 1     | L-3             |

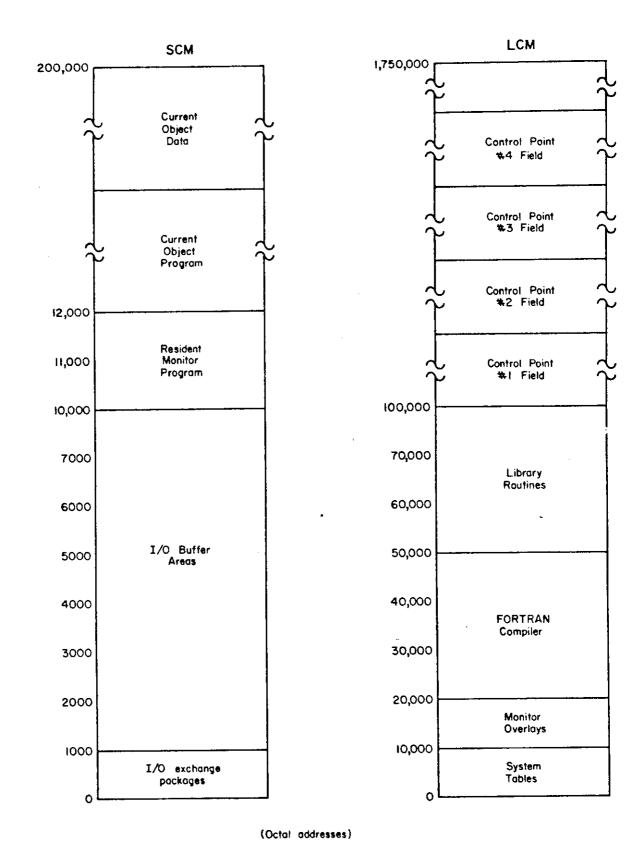

| Operating system 1         | L-4             |

| System monitor 1           | L-4             |

| Object program 1           | L-4             |

| Central processing unit I  | L-5             |

| CPU core memory 1          | L <b>-</b> 5    |

| Computation section        | L-6             |

| Instruction word stack 1   | 8-1             |

| X registers                | L-8             |

| A registers                | L-8             |

| B registers                | L-8             |

| Functional units 1         | -9              |

| Binary arithmetic          | -11             |

| Floating point arithmetic  | -11             |

| Integer multiplication     | 1-15            |

| Integer division           | 1-15            |

| Integer division           | L-15            |

| CPU instruction format     | L- 10<br>I ≥ 10 |

| Storage field protection   | 1-10            |

| Program branching          | 1 JO            |

| Exchange jump              | L-20            |

| Program breakpoint         | L⇔ZZ            |

| Error exits 1              | L-22            |

| CPU input-output section 1 | L-23            |

| Weat cime clock            | 1-26            |

| Real time interiore        | L-26            |

| External interrupt 1       | L-26            |

| System dead start 1        | L-27            |

| System operation           | L-27            |

# PART 2: CPU DESCRIPTION

| Control flag names         2-2           Data register names         2-2           Control condition names         2-3           Instruction stack         2-3           Instruction issue         2-13           Boolean unit         2-24           Normalize unit         2-24           Normalize unit         2-36           Floating add unit         2-33           Floating multiply unit         2-43           Floating divide unit         2-50           Population count unit         2-58           Increment unit         2-60           Branch instructions         2-64           Exchange sequence         2-72           Program status register         2-80           X registers         2-80           A registers         2-96           A registers         2-104           RAS register         2-104           FLS register         2-104           FLS register         2-105           FLL register         2-105           FLL register         2-105           FLL register         2-105           SCM address stack         2-105           SCM banks         2-118           Storage | Introduction                      | 2-0          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------|

| Data register names         2-2           Control condition names         2-2           Instruction stack         2-3           Instruction issue         2-13           Boolean unit         2-21           Shift unit         2-24           Normalize unit         2-29           Long add unit         2-33           Floating add unit         2-36           Floating divide unit         2-50           Population count unit         2-58           Increment unit         2-60           Branch instructions         2-64           Exchange sequence         2-72           Program status register         2-80           X registers         2-88           B registers         2-88           B registers         2-100           RAS register         2-104           FLS register         2-104           RAL register         2-105           NEA register         2-105           NEA register         2-105           SCM banks         2-106           SCM banks         2-118           Storage address stack         2-122           SCM data distribution         2-128           SCM destinatio | Control flag names                | Z <b>– Z</b> |

| Control condition names       2-3         Instruction stack       2-3         Instruction issue       2-13         Boolean unit       2-21         Shift unit       2-24         Normalize unit       2-29         Long add unit       2-33         Floating multiply unit       2-43         Floating divide unit       2-50         Population count unit       2-58         Increment unit       2-60         Branch instructions       2-64         Exchange sequence       2-72         Program status register       2-80         X registers       2-88         B registers       2-96         A registers       2-100         Supporting registers       2-104         RAS register       2-104         FLI register       2-105         FLI register       2-105         SEA register       2-105         SEA register       2-105         SEA register       2-105         SCM banks       2-108         Storage word stack       2-109         SCM data distribution       2-128         SCM data distribution control unit       2-135         Exchange destina                                            | Data register names               | 2-2          |

| Instruction issue       2-13         Boolean unit       2-21         Shift unit       2-24         Normalize unit       2-29         Long add unit       2-33         Floating add unit       2-43         Floating divide unit       2-50         Population count unit       2-50         Population count unit       2-60         Branch instructions       2-64         Exchange sequence       2-72         Program status register       2-80         X registers       2-80         A registers       2-96         A registers       2-100         Supporting registers       2-104         FLS register       2-104         RAL register       2-105         FLL register       2-105         SEA register       2-105         SEA register       2-105         SCM aregister       2-105         SCM aregister       2-105         SCM aregister       2-105         SCM aregister       2-105         SCM banks       2-118         Storage word stack       2-122         SCM data distribution       2-128         SCM destination control unit                                                            | Control condition names           | 2-2          |

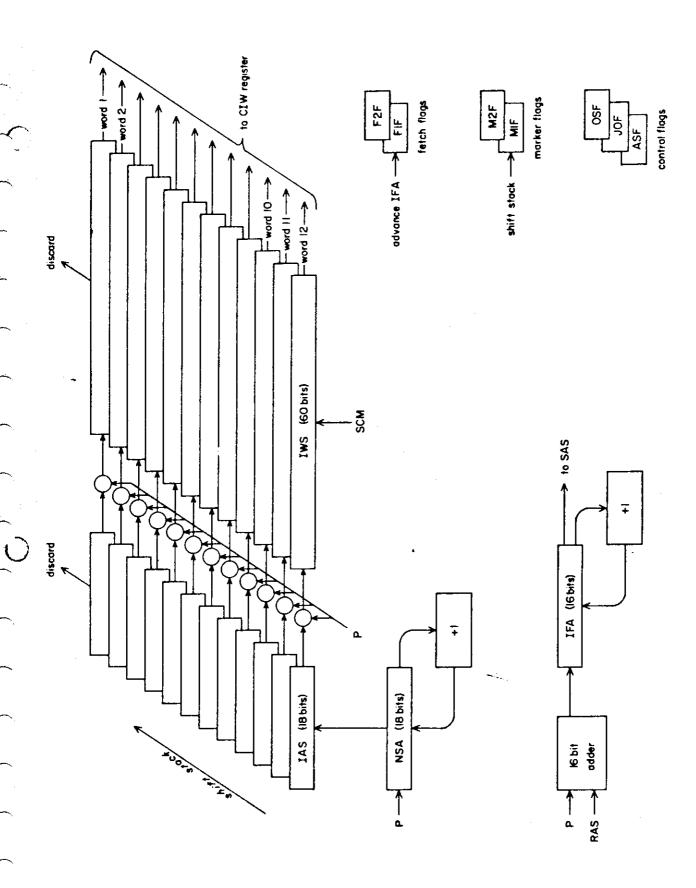

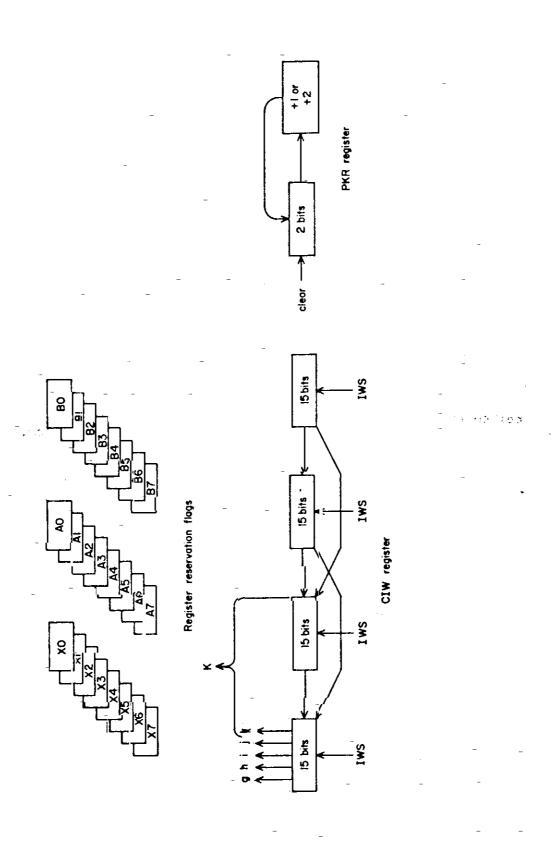

| Instruction issue   2-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Instruction stack                 | 2-3          |

| Boolean unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Instruction issue                 | 2-13         |

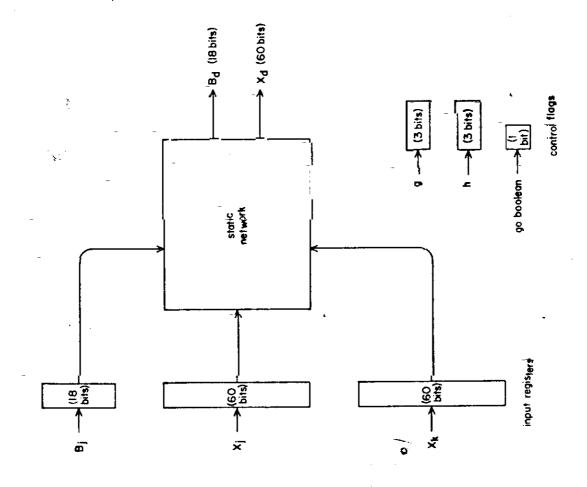

| Shift unit       2-24         Normalize unit       2-39         Long add unit       2-36         Floating add unit       2-43         Floating divide unit       2-50         Population count unit       2-58         Increment unit       2-60         Branch instructions       2-64         Exchange sequence       2-72         Program status register       2-80         X registers       2-88         B registers       2-96         A registers       2-104         RAS register       2-104         FLS register       2-104         RAL register       2-105         NEA register       2-105         EEA register       2-105         SEA register       2-105         SCM actination comenory       2-106         SCM banks       2-118         Storage word stack       2-109         SCM destination control unit       2-131         Exchange destination control unit       2-131         Exchange destination control unit       2-138                                                                                                                                                              | Paglogn unit                      | 2-21         |

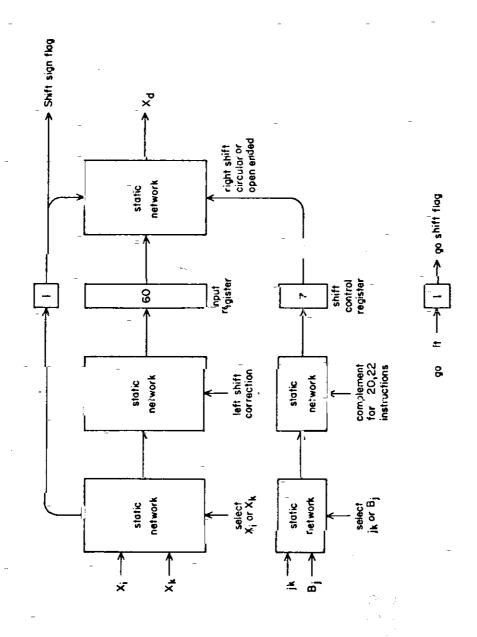

| Normalize unit       2-33         Long add unit       2-36         Floating add unit       2-43         Floating multiply unit       2-50         Population count unit       2-58         Increment unit       2-60         Branch instructions       2-64         Exchange sequence       2-72         Program status register       2-80         X registers       2-88         B registers       2-96         A registers       2-100         Supporting registers       2-104         RAS register       2-104         RAL register       2-105         FLL register       2-105         NEA register       2-105         SEA register       2-105         SCM data distribution       2-128         SCM destination control unit       2-138         SCM destination control unit       2-135         Exchange destination con                                            | Chift unit                        | 2-24         |

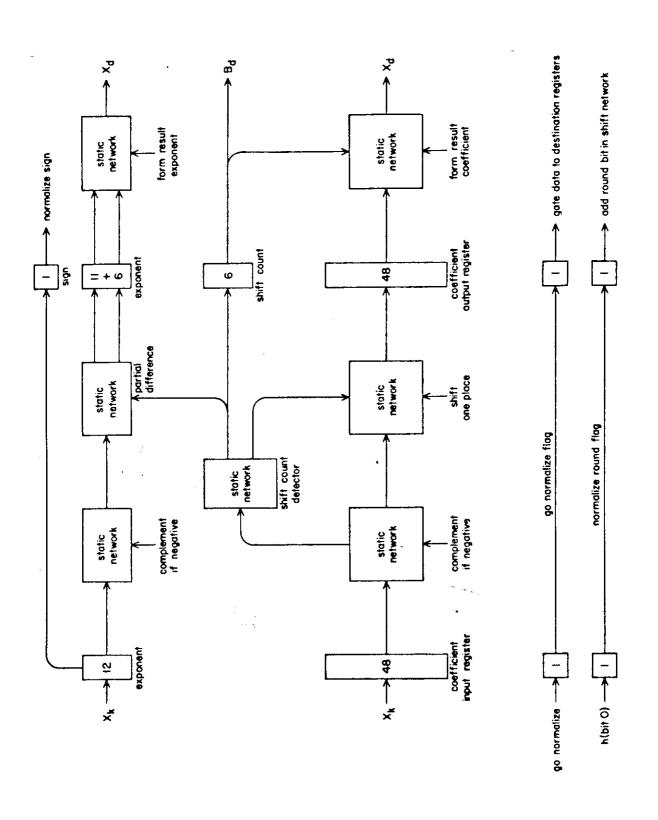

| Long add unit       2-36         Floating add unit       2-43         Floating multiply unit       2-50         Population count unit       2-58         Increment unit       2-60         Branch instructions       2-64         Exchange sequence       2-72         Program status register       2-80         X registers       2-88         B registers       2-96         A registers       2-100         Supporting registers       2-104         RAS register       2-104         RAL register       2-105         FLL register       2-105         NEA register       2-105         SEA register       2-105         SCM register       2-105         SCM banks       2-106         SCM banks       2-118         Storage word stack       2-109         SCM data distribution       2-122         SCM destination control unit       2-131         Exchange destination control unit       2-135         Input/Output section       2-138                                                                                                                                                                    | Namelia wit                       | 2-29         |

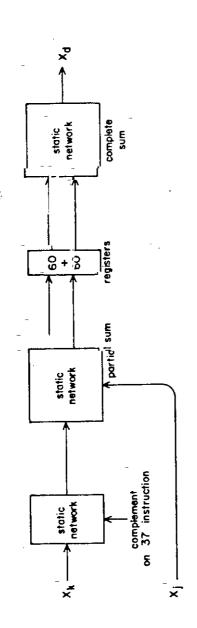

| Floating add unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Tong odd unit                     | 2-33         |

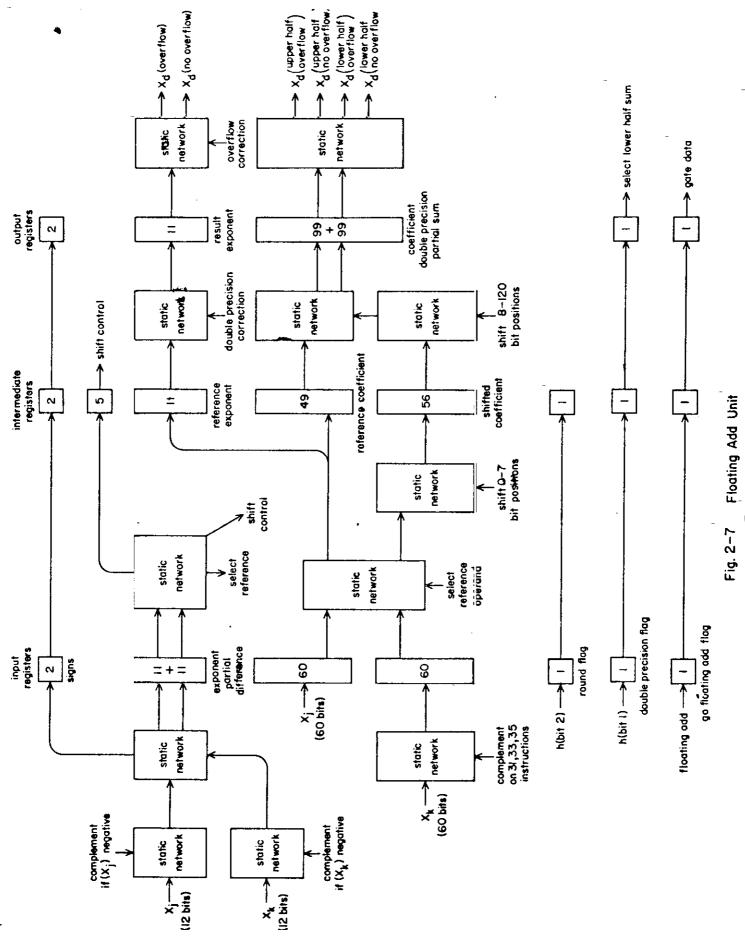

| Floating multiply unit       2-43         Floating divide unit       2-50         Population count unit       2-58         Increment unit       2-60         Branch instructions       2-64         Exchange sequence       2-72         Program status register       2-80         X registers       2-88         B registers       2-96         A registers       2-100         Supporting registers       2-104         RAS register       2-104         FLS register       2-104         RAL register       2-105         FLA register       2-105         NEA register       2-105         SEA register       2-105         EEA register       2-105         SCM barks       2-106         SCM banks       2-118         Storage word stack       2-122         SCM destination control unit       2-131         Exchange destination control unit       2-135         Innut/Output section                                                  | Floating add unit                 | 2-36         |

| Floating divide unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Floating multiply unit            | 2-43         |

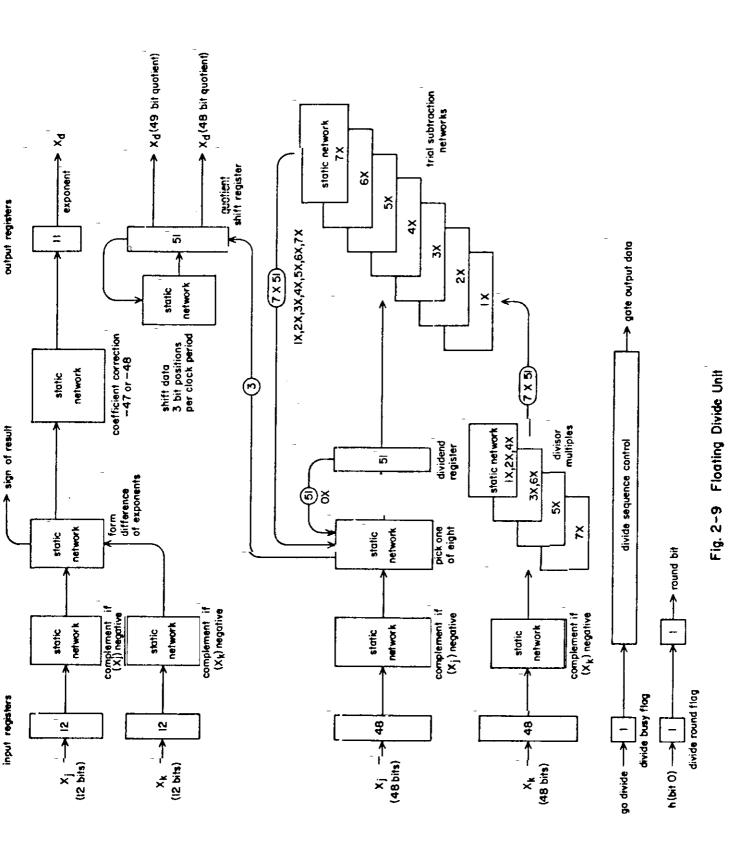

| Population count unit       2-38         Increment unit       2-60         Branch instructions       2-64         Exchange sequence       2-72         Program status register       2-80         X registers       2-88         B registers       2-96         A registers       2-100         Supporting registers       2-104         RAS register       2-104         RAL register       2-105         FLL register       2-105         NEA register       2-105         EEA register       2-105         SEA register       2-105         SCM address stack       2-106         Scomall core memory       2-107         Storage address stack       2-107         Scom banks       2-118         Storage word stack       2-122         SCM data distribution       2-128         SCM destination control unit       2-131         Exchange destination control unit       2-135         Input/Output section       2-138                                                                                                                                                                                         | Floating divide unit              | 2-50         |

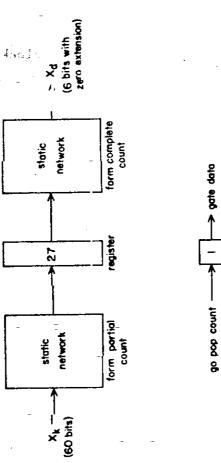

| Increment unit       2-64         Branch instructions       2-64         Exchange sequence       2-72         Program status register       2-80         X registers       2-88         B registers       2-96         A registers       2-100         Supporting registers       2-104         RAS register       2-104         FLS register       2-105         FLI register       2-105         NEA register       2-105         NEA register       2-105         Small core memory       2-106         Small core memory       2-107         Storage address stack       2-109         SCM banks       2-118         Storage word stack       2-122         SCM data distribution       2-128         SCM destination control unit       2-131         Exchange destination control unit       2-135         Input/Output section       2-138                                                                                                                                                                                                                                                                      | Population count unit             | 2-58         |

| Branch instructions       2-04         Exchange sequence       2-72         Program status register       2-80         X registers       2-88         B registers       2-100         A registers       2-104         RAS register       2-104         FLS register       2-105         RAL register       2-105         NEA register       2-105         NEA register       2-105         SEA register       2-106         Small core memory       2-106         Small core memory       2-107         Storage address stack       2-109         SCM banks       2-118         Storage word stack       2-122         SCM data distribution       2-128         SCM destination control unit       2-131         Exchange destination control unit       2-135         Input/Output section       2-138                                                                                                                                                                                                                                                                                                               | The remark unit                   | 2-60         |

| Exchange sequence       2-72         Program status register       2-88         X registers       2-96         A registers       2-100         Supporting registers       2-104         RAS register       2-104         FLS register       2-105         FLL register       2-105         NEA register       2-105         EEA register       2-106         BPA register       2-106         Small core memory       2-107         Storage address stack       2-109         SCM banks       2-118         Storage word stack       2-122         SCM destination control unit       2-128         SCM destination control unit       2-131         Exchange destination control unit       2-135         Input/Output section       2-138                                                                                                                                                                                                                                                                                                                                                                            | Propositions                      | 2-64         |

| Program status register       2-88         X registers       2-96         A registers       2-100         Supporting registers       2-104         RAS register       2-104         FLS register       2-105         RAL register       2-105         NEA register       2-105         EEA register       2-106         BPA register       2-106         Small core memory       2-107         Storage address stack       2-109         SCM banks       2-118         Storage word stack       2-122         SCM destination control unit       2-131         Exchange destination control unit       2-135         Input/Output section       2-138                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Exphance sequence                 | 2-72         |

| X registers       2-86         B registers       2-100         Supporting registers       2-104         RAS register       2-104         FLS register       2-105         FLL register       2-105         NEA register       2-105         EEA register       2-106         Small core memory       2-106         Scom banks       2-118         Storage word stack       2-122         SCM data distribution       2-128         SCM destination control unit       2-131         Exchange destination control unit       2-135         Input/Output section       2-138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Drogram status register           | Z-0U         |

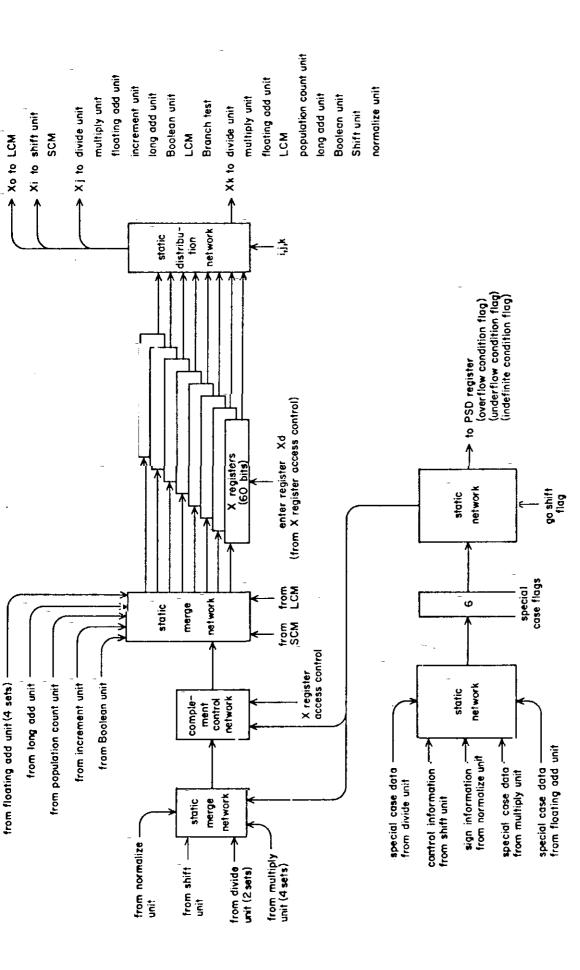

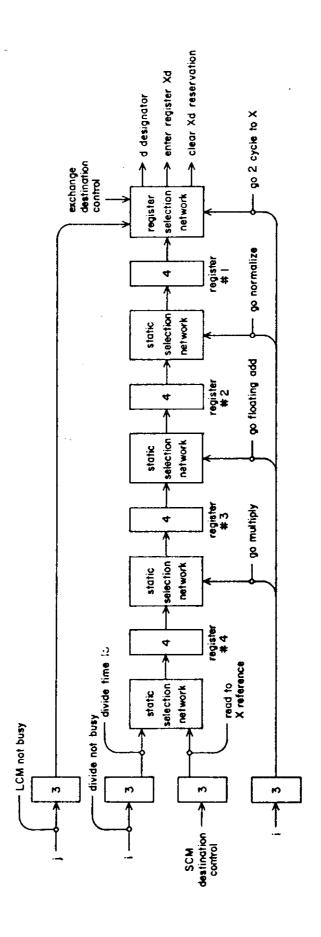

| B registers       2-96         A registers       2-100         Supporting registers       2-104         RAS register       2-104         FLS register       2-105         FLL register       2-105         NEA register       2-105         EEA register       2-106         Small core memory       2-106         Scom banks       2-109         SCM banks       2-118         Storage word stack       2-122         SCM data distribution       2-128         SCM destination control unit       2-131         Exchange destination control unit       2-135         Input/Output section       2-138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Y registers                       | 2-88         |

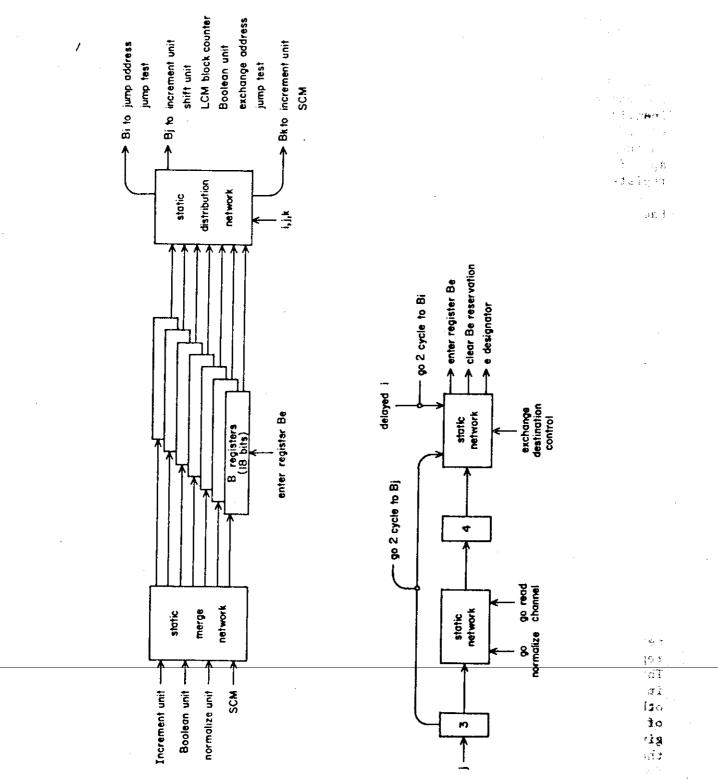

| A registers       2-100         Supporting registers       2-104         RAS register       2-104         FLS register       2-105         RAL register       2-105         NEA register       2-105         EEA register       2-106         BPA register       2-106         Small core memory       2-107         Storage address stack       2-109         SCM banks       2-118         Storage word stack       2-122         SCM data distribution       2-128         SCM destination control unit       2-131         Exchange destination control unit       2-135         Input/Output section       2-138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R registers                       | 2-96         |

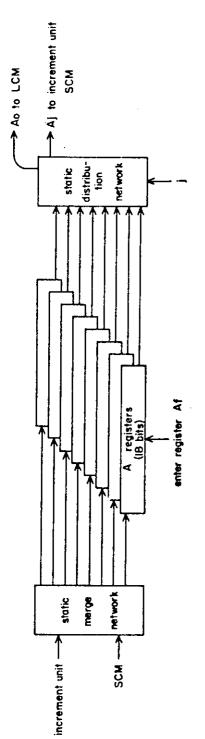

| Supporting registers       2-104         RAS register       2-104         FLS register       2-105         RAL register       2-105         NEA register       2-105         EEA register       2-106         BPA register       2-106         Small core memory       2-107         Storage address stack       2-109         SCM banks       2-118         Storage word stack       2-122         SCM data distribution       2-128         SCM destination control unit       2-131         Exchange destination control unit       2-135         Input/Output section       2-138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | A registers                       | 2-100        |

| RAS register       2-104         FLS register       2-105         RAL register       2-105         NEA register       2-105         EEA register       2-106         BPA register       2-106         Small core memory       2-107         Storage address stack       2-109         SCM banks       2-118         Storage word stack       2-122         SCM data distribution       2-128         SCM destination control unit       2-131         Exchange destination control unit       2-135         Input/Output section       2-138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Comparting registers              | 2-104        |

| FLS register       2-104         RAL register       2-105         FLL register       2-105         NEA register       2-106         BPA register       2-106         Small core memory       2-107         Storage address stack       2-109         SCM banks       2-118         Storage word stack       2-122         SCM data distribution       2-128         SCM destination control unit       2-131         Exchange destination control unit       2-135         Input/Output section       2-138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | DAS register                      | 2-104        |

| RAL register       2-105         FLL register       2-105         NEA register       2-106         EEA register       2-106         Small core memory       2-107         Storage address stack       2-109         SCM banks       2-118         Storage word stack       2-122         SCM data distribution       2-128         SCM destination control unit       2-131         Exchange destination control unit       2-135         Input/Output section       2-138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | FIC register                      | 2-104        |

| FLL register       2-105         NEA register       2-106         EEA register       2-106         Small core memory       2-107         Storage address stack       2-109         SCM banks       2-118         Storage word stack       2-122         SCM data distribution       2-128         SCM destination control unit       2-131         Exchange destination control unit       2-135         Input/Output section       2-138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DAT register                      | 2-105        |

| NEA register       2-105         EEA register       2-106         BPA register       2-107         Storage address stack       2-109         SCM banks       2-118         Storage word stack       2-122         SCM data distribution       2-128         SCM destination control unit       2-131         Exchange destination control unit       2-135         Input/Output section       2-138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | FIT register                      | 2-105        |

| EEA register       2-106         BPA register       2-106         Small core memory       2-107         Storage address stack       2-109         SCM banks       2-118         Storage word stack       2-122         SCM data distribution       2-128         SCM destination control unit       2-131         Exchange destination control unit       2-135         Input/Output section       2-138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | NFA register                      | 2-105        |

| BPA register       2-106         Small core memory       2-107         Storage address stack       2-109         SCM banks       2-118         Storage word stack       2-122         SCM data distribution       2-128         SCM destination control unit       2-131         Exchange destination control unit       2-135         Input/Output section       2-138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | FFA register                      | 2-106        |

| Small core memory       2-107         Storage address stack       2-109         SCM banks       2-118         Storage word stack       2-122         SCM data distribution       2-128         SCM destination control unit       2-131         Exchange destination control unit       2-135         Input/Output section       2-138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RPA register                      | 2-106        |

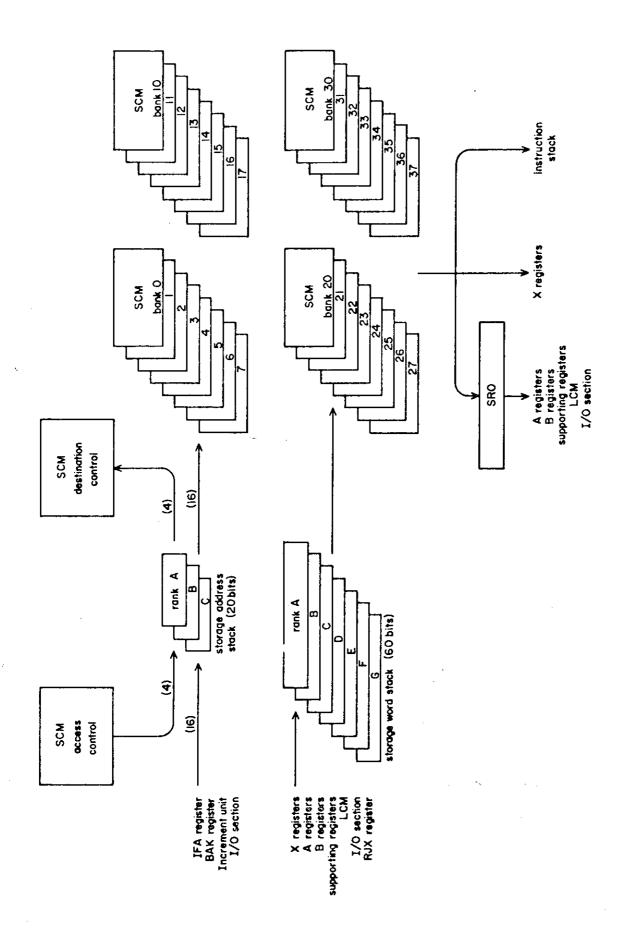

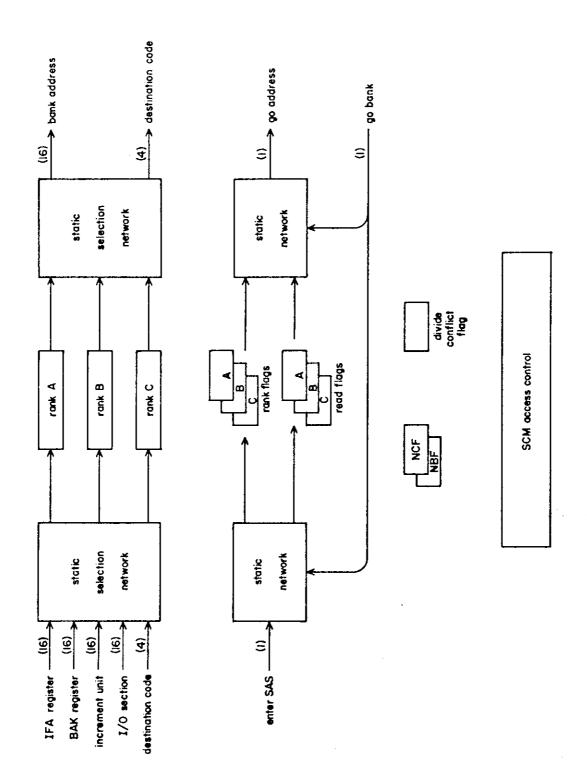

| Storage address stack       2-109         SCM banks       2-118         Storage word stack       2-122         SCM data distribution       2-128         SCM destination control unit       2-131         Exchange destination control unit       2-135         Input/Output section       2-138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Small core memory                 | 2-107        |

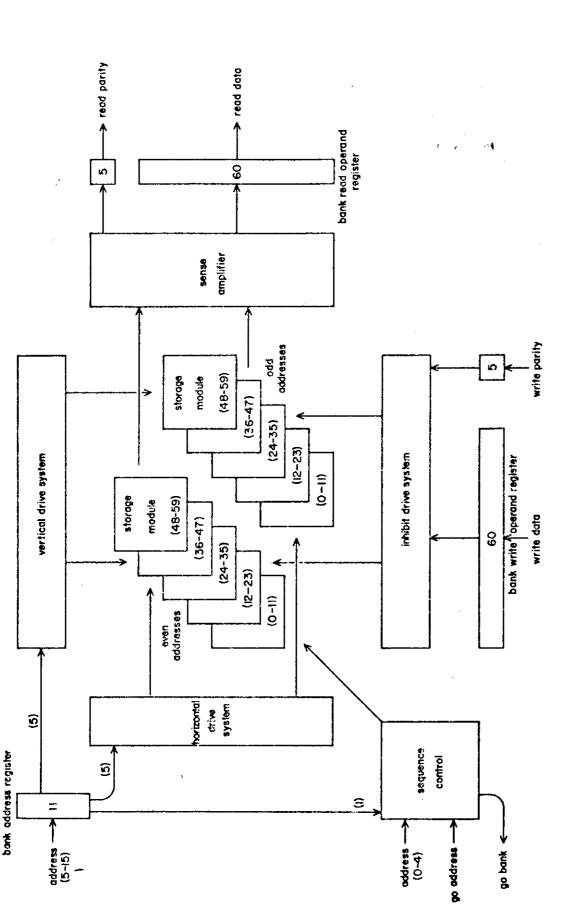

| SCM banks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Starge address stack              | 2-109        |

| Storage word stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CCM hanks                         | 2-118        |

| SCM data distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Change word stack                 | 2-122        |

| SCM destination control unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Scotlage word stack               | 2-128        |

| Exchange destination control unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | om lastication control unit       | 2-131        |

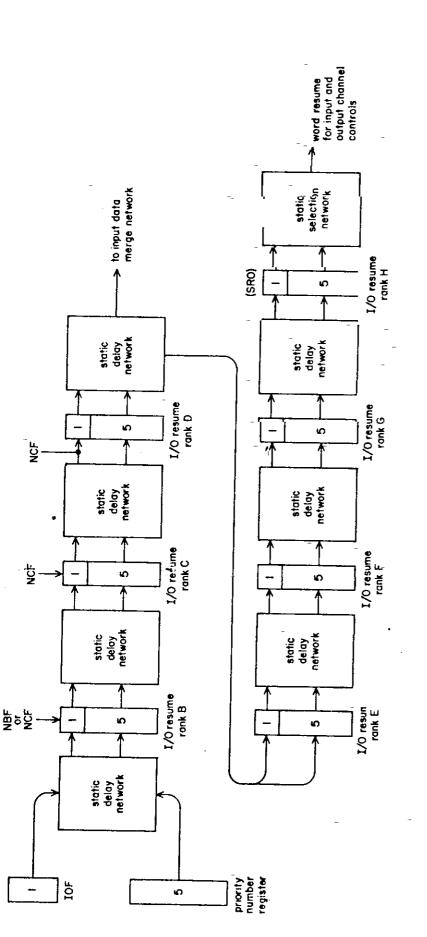

| Input/Output section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SUM destination control unit      | 2-135        |

| Innii / Quebue Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Exchange destination control unit |              |

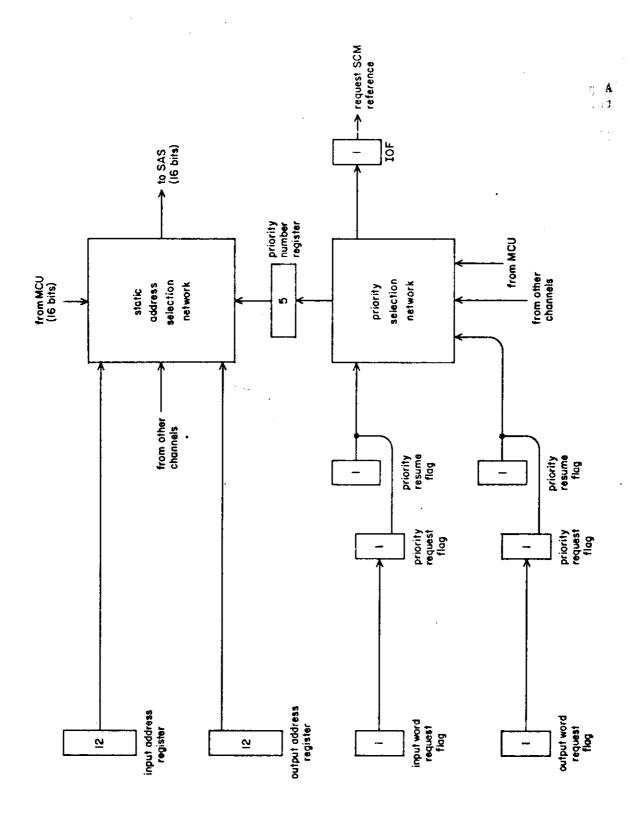

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Channel input control unit        | _            |

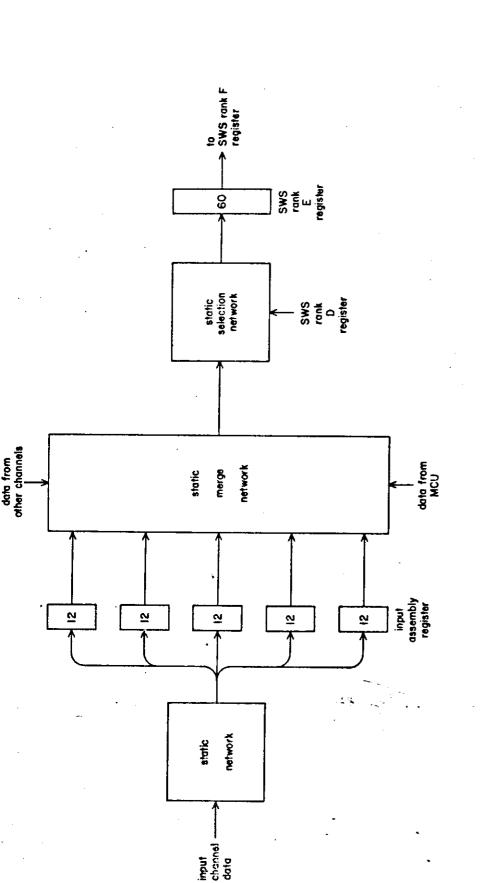

| Input data merge network 2-150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Channel input control unit        |              |

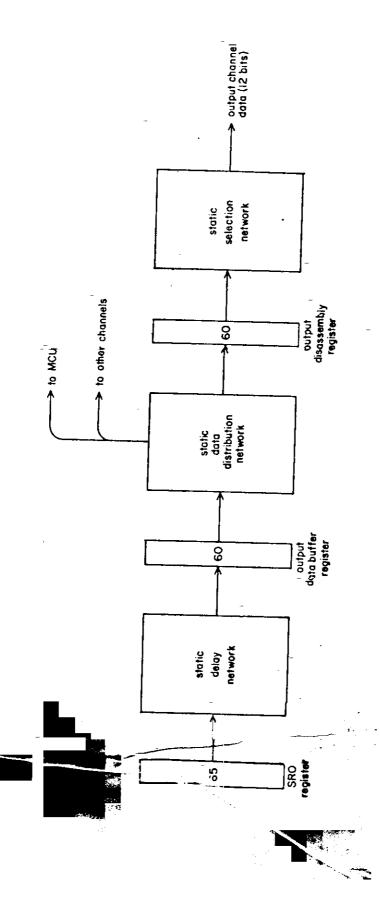

| Input data merge network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Channel output control unit       |              |

# PART 3: CPU INSTRUCTIONS

| Introd         | uction                                   | 3-0          |

|----------------|------------------------------------------|--------------|

| xxx00          | Error exit                               | 3-1          |

| 0100x          | xxxxx Return jump                        | 3-2<br>3-9   |

| 01ljx          |                                          | _            |

| 012jx          |                                          | 3-17         |

| 013jx          | XXXXX Exchange exit (exit mode flag set) | 3-25         |

| 01300          | EXCHANGE EXTE (CXTE mode Trap process)   | 3-36         |

| 014jk          | Read LCM                                 | 3-40         |

| 015jk          | Write LCM                                | 3-44         |

| 0160k          | Reset input buffer                       | 3-47         |

| 016jk          | Read channel input status (j nonzero)    | 3-50         |

| 0170k          | Reset output buffer                      | 3-52         |

| 017jk          | Read channel output status (j nonzero)   | 3-56         |

| 02i0x          | xxxxx Jump to B + K                      | 3-58         |

| 030jx          | xxxxx Branch on X zero                   | 3-64         |

| 031jx          | xxxxx Branch on X nonzero                | 3-70         |

| 032jx          |                                          | 3-71<br>3-72 |

| 033jx          |                                          | 3-72         |

| 034jx          |                                          | 3-74         |

| 035jx          | xxxxx Branch on X not in range           | 3-74         |

| 036jx          |                                          |              |

| 037jx          |                                          | 3-76<br>3-77 |

| 04ijx          |                                          | 3-77         |

| 05ijx          |                                          |              |

| _              | xxxxx Branch on B .GE. B                 | 3-85<br>3-86 |

| -              | xxxxx Branch on B .LT. B                 | 3-87         |

| 10ij0          | Copy                                     | 3-89         |

| llijk          | Logical product                          |              |

| 12ijk          | Logical sum                              | 3-91<br>3-93 |

| 13ijk          | Logical difference                       | 3-95         |

| 1410k          | Copy complement                          | 3-97         |

| 15ijk          | Logical product with complement          | 3-99         |

| 16ijk          | Logical sum with complement              |              |

| 17ijk          | Logical difference with complement       | 3-101        |

| 20ijk          | Left shift X by jk                       | 3-103        |

| 21ijk          | Right shift X by jk                      | 3-103        |

| 22 <b>i</b> jk | Left shift X by B                        |              |

| 23ijk          | Right shift X by B                       | -            |

| 241jk          | Normalize X to X, B                      |              |

| 251Jk          | Round normalize X to X, B                |              |

| 261 jk         | Unpack X to X, B                         |              |

| 271jk          | Pack X, B to X                           | 3-124        |

| 30ijk           | Floating sum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-127 |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 31ijk           | Floating difference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3-131 |

| 32ijk           | Floating double precision sum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3-135 |

| 33i jk          | Floating double precision difference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3-140 |

| 34ijk           | Round floating sum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-145 |

| 35ijk           | Round floating difference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3-151 |

| 36i jk          | Integer sum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-157 |

| 37ijk           | Integer difference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-159 |

| 401 jk          | Floating product                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-161 |

| 4lijk           | Round floating product                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-165 |

| 421jk           | Floating double precision product                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 3-168 |

| 43i jk          | Form mask jk                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-172 |